OFweek

1 系统总体设计方案

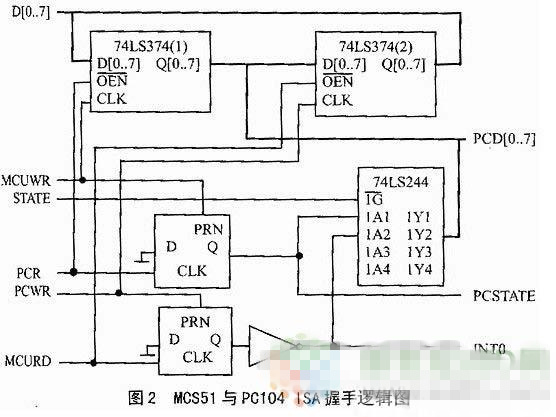

本系统用CLPD实现单片机与PC104 ISA总线接口的并行通信。由于PC104主要完成其它方面的数据采集工作,只是在空闲时才能接收单片机送来的数据,所以要求双方通信的实时性很强,但数据量不是很大。因此,在系统设计中单片机中断方式接收数据,PC104采用查询方式接收数据。系统设计方案如图1所示。

在图1单片机部分,D[0..7]是数据总线,A[0..15]是地址总线,RD和WR分别是读写信号线,INT0是单片机的外部中断。当单片机的外部中断信号有效时,单片机接收数据。

在CPLD部分,由一片MAX7000系列中的EPM7128LSC84来实现,用来完成MCS51与PC104ISA总线接口之间的数据传输、状态查询及延时等待。

在PC104 ISA部分,只用到ISA的8位数据总线D[0..7],A[0..9]是PC104的地址总线;IOW和IOR是对指定设备的读写信号;AEN是允许DMA控制地址总线、数据总线及读写命令线进行DMA传输,及对存储器和I/O设备的读写;IOCHRDY是I/O就绪信号,I/O通道就绪为高,此时处理机产生的存储器读写周期为4个时钟周期,产生的I/O读写周期和DMA字节传输均需5个时钟周期,MCS51通过置此信号为低电平来使CPU插入等待周期,从而延长I /O周期;SYSCLK是系统时钟信号,是为了与外部设备保持同步;RESETDR是上电复位或系统初始化逻辑,是系统总清信号。

关注我们

公众号:china_tp

微信名称:亚威资讯

显示行业顶级新媒体

扫一扫即可关注我们