为了了解Micro LED磊晶片转移的问题,笔者查阅资料发现一家叫X-Celeprint的公司曾在2014年推出了一门技术叫μTP的技术。据悉,该μTP技术作为一项先进的微装配技术,可以使数百个小型(最适宜尺寸为亚毫米级)器件在同一时间内精确移动。

μTP技术最初是由美国Illinois University的John A. Rogers等人利用牺牲层湿蚀刻和PDMS转贴的技术,将Micro LED转贴至可挠式基板或玻璃基板上来制作Micro LED阵列的技术,该技术于2006年Spin-out给Semprius公司,而2013年X-Celeprint获得Semprius技术授权,并于2014年初开始正式运营。

什么是μTP技术

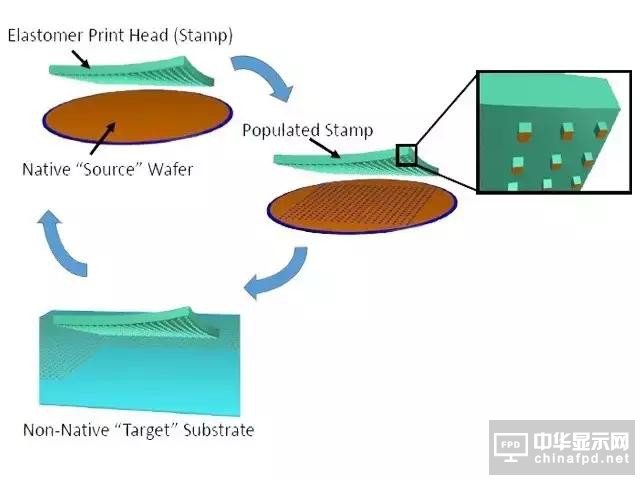

μTP技术,简单的来说,就是使用弹性印模(stamp)结合高精度运动控制打印头,有选择的拾取(pick-up)微型元器件的阵列,并将其打印(printing)到目标基板上。

具体来说就是,首先在“源”晶圆上制作微型芯片,然后通过移除半导体电路下面的牺牲层(sacrificial layer)进行“释放”(Release),使微型芯片脱离原来的基板。随后,用一个与“源”晶圆相匹配的微结构弹性印模来拾取微型芯片,并将其转移到目标基板上。

该技术可以通过改变打印头的速度,选择性地调整弹性印模和被转移器件之间的黏附力,从而准确地控制装配工艺。当印模移动较快时黏附力增大,从而使被转移元件脱离源基板;相反地,当印模远离键合界面且移动较慢时,黏附力变得很小,被打印元件便会脱离印模,然后被转印在目标基板。

上文提到的印模可以通过定制化的设计实现单次拾取和打印多个器件,从而短时间内高效的转移成千上万个器件,因此这项工艺流程可以实现大规模并行处理。

μTP技术实际应用中的工艺流程

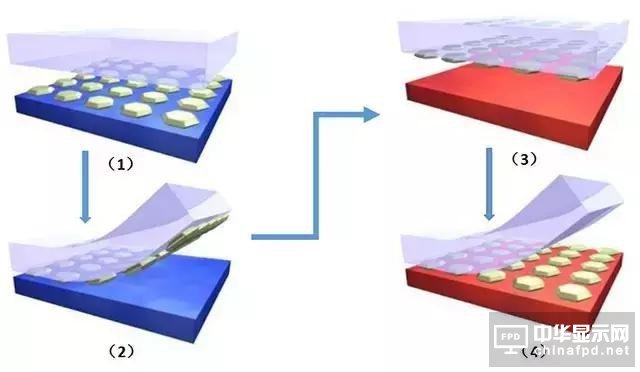

微转印工艺流程:图1:弹性印模接近晶圆;图2:弹性印模拾起芯片;图3:弹性印模接近目标基板;图4:印模将芯片“印刷”(放置)在目标基板上

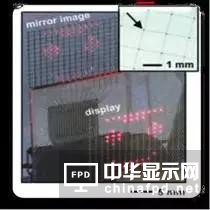

据X-celeprint此前表示,该技术已经在众多“可印刷”微型器件中得到验证,包括激光器、LED、太阳能电池和各种材料(硅、砷化镓、磷化铟、氮化镓和包括金刚石在内的介电薄膜)的集成电路。

基于GaAs的红色microLED印刷案例

μTP技术转印器件的原理过程

大多数情况下,需要转印的半导体器件首先会从“源”晶圆上得到释放,该方法利用了器件层下方的牺牲层(sacrificial layer)。

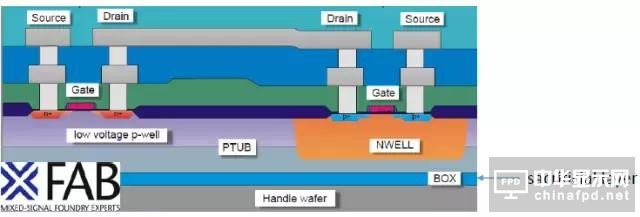

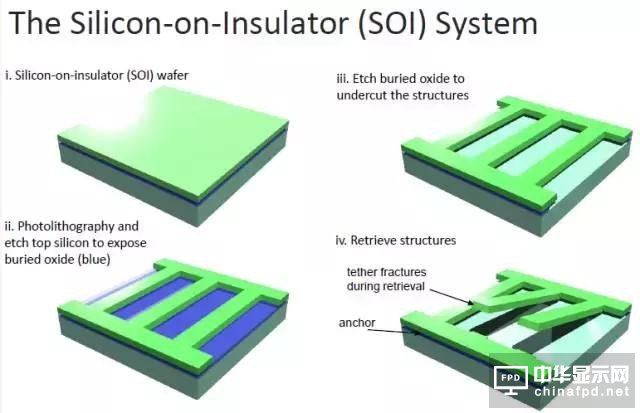

绝缘体上硅(SOI)晶圆的结构是在一层1微米厚的氧化层(Box: Barrier Oxide)上面制备一层5微米厚的单晶硅层。然后在单晶硅层上面采用标准SOI晶体管加工工艺制备各种器件和集成电路。不难看出SOI晶圆的氧化层可以作为天然的牺牲层,所以它将会是一种非常方便、随时可用的“源”晶圆。

简单介绍一下SOI加工工艺:

首先按照CMOS工艺标准,用光刻和刻蚀的工艺对SOI晶圆表面的单晶硅层进行图形化,露出下面的Box层。然后对图形化后的单晶硅进行封装保护。用氢氟酸刻蚀去除器件下方的BOx层,在此过程中ILD和布线层受到保护而不会损伤。

当器件下方的Box层被完全去除后,器件将会从晶圆中完全脱离出来,并通过器件层中的栓绳(Tether)来进行位置固定。在转印期间,栓绳(Tether)可以通过可控的方式断裂或切开。

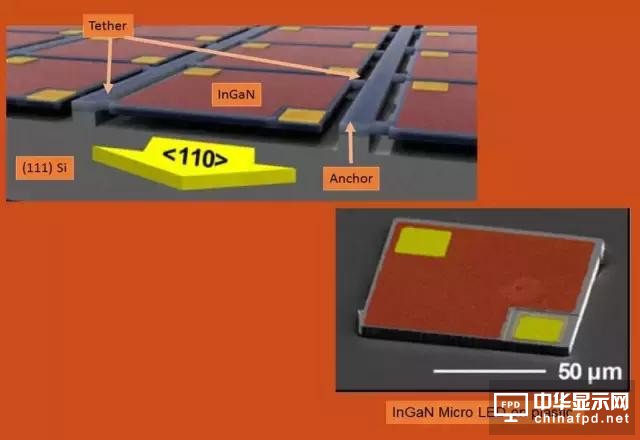

氮化镓晶体管在si晶圆(111)制作而成,反应离子刻蚀(RIE)将通过通孔穿过器件层,向下直至硅基板,实现单个器件的分离。在该步骤中使用了二氧化硅掩膜。通过等离子体增强化学气相沉积法(PECVD)将氮化硅层沉积。氮化硅层不仅可以钝化器件侧壁,也可以用于锚定(Anchor)和栓绳(Tether)结构的形成。

而在氮化镓芯片在印刷前,先会在COMS晶圆上施以一层半导体薄膜级树脂。到了微转印完成后,底层树脂则被固化,再通过钨化钛和铝金属叠层溅射沉积,到减厚湿法刻蚀,最终形成器件的连接。(技术审核:中山大学 刘召军博士;图片来源:X-Celeprint)

关注我们

公众号:china_tp

微信名称:亚威资讯

显示行业顶级新媒体

扫一扫即可关注我们